|

|

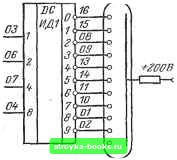

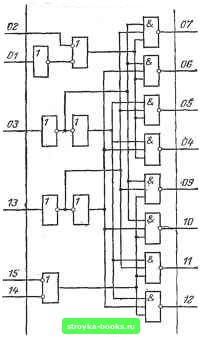

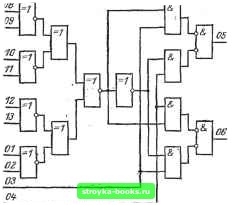

Главная Развитие народного хозяйства [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [ 16 ] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] кий потенциал. В счетчике возможна предварительная запись числа путем подачи кода числа на информационные входы и нулевого импульса на вход предварительной записи (вывод ), следующего с некоторым отставанием (не менее 20 не) от информаци-, онных сигналов. Установка нулевого положения счетчика осуществляется подачей сигнала высокого уровня на вход 14. Делитель частоты с переменным коэффициентом деления К155ИЕ8 состоит из шестиразрядного двоичного счетчика и логической схемы, которая обеспечивает вы„ачу на вход заданного количества импульсов (см. рис. 1-61, ж). Количество импульсов на выходе при подаче на счетный вход {09) последовательности из 64 импульсов определяют по формуле = V 32-25-f 1/16.2«+ V8-23-f -f V 4-22-fV2-24-V 1-20. Таким образом, комбинация уровней логических сигналов на входах умножения Vl(04), V2(01), V4(14), V8(15), V16(02), \32(03) определяет заданную сумму импульсов на выводах 05, 06. При этом на выводы , 12 должно быть подано напряжение «логический нуль». На выводе 07 получают нулевой импульс после подачи на вход 09 64 импульсов. Четырехразрядный универсальный регистр сдвига К155ИР1 (см. рис. 1-62) организован на двухступенчатых PS-триггерах с входной логикой. Регистр сдвига позволяет реализовать следующие режимы работы: запись информации параллельным кодом, сдвиг вправо, сдвиг влево. Управление режимом работы осуществляется по входам Vl(Ol), V2(06), С1(09), С2(08). Для записи в регистр информации параллельным кодом следует на вход управления режимом V2 подать напряжение «логическая единица» («лог. 1»), а на вход С2 - напряжение «логический нуль» («лог. О»); информационные сигналы подаются на входы D1-D4 {02, 03, 04, 05). При этом сигналы на входах VI и С1 {01, 09) могут быть любыми. Для сдвЕга информации вправо тактовые импульсы подаются на вход С2. При этом на входе V2 следует поддерживать напряжение «лог. 1». При операциях с данными, представленными в последовательном коде, входная информация в виде последовательности импульсов подается на вход VI, тактовые импульсы подаются на вход синхронизации С1, а на входах V2, D1-D4 ьоддерживается напряжение «лог. О». Для сдвига информации влево на вход V2 подается напряжение «лог. 1». При этом входы параллельной записи используются для организации цепей сдвига, для чего, выход последнего разряда соединяется с входом параллельного кода предыдущего разряда, его выход - с аналогичным входом предшествующего разряда и т. д. Входом после- довательного кода в этом случае служит (зход параллельного кода последнего разряда. Применяя дополнительный внешний инвертор, можно с помощью регистра сдвига осуществлять деление частоты на два, четыре, шесть, восемь или три, пять, семь. В этом случае на входе V2 поддерживается напряжение «лог. О», входные импульсы подаются на вход синхронизации С/, а выходные снимаются с соответствующего разрядного выхода, который соединяется через внешний инвертор с входом VI. При этом состояние входов С2, D1-D4 может быть любым. При делении на три, пять, семь в цепь обратной связи включается элемент И-НЕ, на входы которого подаются сигналы с выходов первого и второго разрядов при делении на три, второго и третьего разрядов при делении н-а пять, третьего и четвертого при делении на семь. Оперативное запоминающее устройство (ОЗУ) на 16 бит К155РУ1 (см. рис. 1-63. а) имеет в своем составе 16 ячеек памяти (организация 16X1), два усилителя записи и два усилителя считывания. Двухкоордкнатная система выборки адреса {А1-А4 и В1-В4) позволяет делать выборку информации за цикл (табл. 1-13). Микросхема работает в следующих режимах: режим записи, режим хранения, режим считывания. Запись информации в ячейку памяти осуществляется при обращении к соответствующей ячейке (выбор адреса) и подаче напряжения «лог. 1» на вход усилителя записи нуля -при записи «лог. О» или усилителя записи единицы -при записи «лог. 1». В режиме хранения на адресные входы и выходы усилителей записи подается напряжение «лог. О», при ЭТОМ на выходах усилителей считывания присутствуют сигналы «лог. 1» (выходные транзисторы закрыты). Считывание информации, записанной в ячейке памяти, происходит при обращении к соответствующей ячейке (выбор адреса) и подаче напряжения «лог. О» на входы усилителей записи. Обращение к ячейке памяти происходит при одновременной подаче сигналов «лог. 1» на соответствующие данной ячейке адресные входы А и В. Считывание информации происходит без ее разрушения. Выходной усилитель считывания выполнен по схеме с открытым коллектором и допускает объединение типа «проводное ИЛИ». Одновременные запись и считывание невозможны, так как они используют одни н те же входы. Оперативное запоминающее устройство. Запись и считывание ОЗУ К155РУ2 на 64 бит (16X4) (см. рис. 1-63, б) производятся по 16 адресам. Четырехразрядная информация записывается в ОЗУ параллельным кодом через четыре усилителя записи, считывание производится также в параллельном коде через четыре усилителя считывания. Таблица 1-13 Таблица состояний ОЗУ К155РУ!

Функциональное назначение выводов микросхемы: 01 - вход первого разряда адреса; 02 - вход разрешения выборки; 03 - вход разрешения записи; 04 - вход данных (первый разряд); 05 - выход считывания (первый разряд); 06-вход данных (второй разряд); 07 -выход считывания (второй разряд); 08 - общий; 09 - выход считывания (третий разряд); /О -вход данных (третий разряд); И--выход считывания (четвертый разряд); 12 - вход данных (четвертый разряд); /3-вход четвертого разряда адреса; 14 - вход третьего разряда адреса; 15 - вход второго разряда адреса; 16 - питание. Преобразователь двоично-десятичного кода в десятичный для управления высоковольтным индикатором К155ИД1 (см. рис. 1-64, а) содержит в себе дешифратор из двоично-десятичного кода в десятичный с выходными высоковольтными ключами. На рнс. 1-76 приведен пример использования микросхемы К155ИД1 для работы на высоковольтный индикатор. Дешифратор-демультиплексор К155ИДЗ (см. рис. 1-64,6) служит в основном для преобразования двоичного кода в код 1 из 16. Процесс дешифрирования происходит только при наличии сигналов с напряжением «лог. О» на двух стробирующих входах V0, VI (18, 19). Сдвоенный дешифратор-мультиплексор 2-4 К155ИД4 (см. рис. 1-64, б) может иметь два различных применения: два дешифратора 2-4, один дешифратор 3-8. Логическая структура микросхемы К155ИД4, приведенная на рис. 1-77, поясняет ее принцип действия. Управляющие входы VI, V2 (01, 14) осуществляют вклю-  Рис. 1-76- Схема цифровой индикации с использованием микросхемы К155ИД1.  Рис. 1-77. Логическая структура дешифратора-мультиплексора КМ155ИД4. чение одного из дешифраторов. Входы V3, \4 (02, 15) служат для стробирования. При подаче.напряжения «лог. 1» на входы О/,/4 работает первый дешифратор. При подаче напряжения «лог. О» на эти входы работает второй дешифратор. Стробирование производится нулевыми сигналами. Второй вариант использования микросхемы- дешифратор на 8. Для этой цели объединяют входы 01 и 14, на них подается третий разряд двоичного кода.  Рис. 1-78. Логическая структура микросхемы контроля четности и нечетности КМ155ИП2. Коммутатор восьми каналов на один К155КП5 (см. рис. 1-65, а) выдает инверсный сигнал на выходе, при этом коммутируется канал, параллельный двоичный код номера которого подается иа входы \1(10), V2(09), V3(08). Коммутатор восьми каналов на один со стробированием К155КП7 (см. рис. 1-65,6) имеет на выходе прямой и инверсный сигналы; параллельный код номера канала подается на входы VI (11), V2(10), V3(09), выходной сигнал появляется при наличии стробирующего сигнала с уровнем «лог. О». На рис. 1-78 приведена логическая структура элемента контроля четности и нечетности К155ИП2, поясняющая принцип действия микросхемы. Преобразователь двоично-десятичного кода в двоичный К155ПР6 (см. рис. 1-67, с) представляет собой ЗУ, предназначенное для длительного хранения постоянной информации объемом 256 бит с организацией 32 слов по 8 разрядов. ЗУ работает только в режиме хранения и считывания. Микросхема состоит из матрицы 32X8 запоминающих ячеек и схем управления, включающих в себя адресные формирователи, входной дешифратор, схему разрешения выборки и выходные усилители считывания. Программирование ЗУ осуществляется иа ста- дии производства микросхем и выбора фотошаблонов. В режиме хранения информации сигналы на выходах микросхемы 01, 02, 03, 04, С5, 06, 07, 08, 09 имеют уровень «лог. 1». При подаче сигнала «лог. Ь на вход 15 происходит запрет считывания информации. Вывод 15 служит для упрощения объединения нескольких микросхем в одно ЗУ большой емкости. Микросхема вьшолняет следующие функции преобразования: двоично-десятичного кода в двоичный, двоично-десятичного кода в код, дополнительный к 9, двоично-десятичного кода в код, дополнительный к 10. Преобразователь двоичного кода в двоично-десятичный К155ПР7 (см. рис. 1-67,6) также представляет собой ПЗУ на 256 бит (32X8). Состав микросхемы аналогичен вышеописанной К155Г1Р6 и отличается только количеством выходных усилителей считывания. ПЗУ для преобразования двоичного кода в коды знаков (см. рис. 1-67, е) содержат матрицу 32X32 ячеек памяти и схемы управления, состоящие из адресных формирователей, входных и выходных дешифраторов, усилителей считывания. Программирование ПЗУ осуществляется на стадии производства микросхем. Выходы усилителей считывания выполнены с открытым коллектором, что позволяет осуществить схему генератора символов из перечисленного комплекта микросхем при параллельном соединении их одноименных выходов. Символы выполнены в формате 7X5 по ГОСТ 13052-74*, каждый символ определяется семиразрядным кодом по ГОСТ 13052-74*. 1-21. ОСОБЕННОСТИ КОНСТРУИРОВАНИЯ И ЭКСПЛУАТАЦИИ АППАРАТУРЫ И РЕКОМЕНДАЦИИ ПО ОБЕСПЕЧЕНИЮ ПОМЕХОУСТОЙЧ ИВОСТИ ПРИ КОНСТРУИРОВАНИИ УСТРОЙСТВ НА МИКРОСХЕМАХ К155 Разводка питающего напряжения узлов и блоков должна производиться проводниками с возможно низким сопротивлением. На платах в цепях питания необходимо предусматривать установку развязывающих конденсаторов из расчета не менее 0,1 мкФ на микросхему для исключения влияния низкочастотных помех. Конденсатор устанавливается вблизи разъема. Развязывающие емкости по высокой частоте должны быть равномерно распределены по всей площади печатной платы из расчета один конденсатор на группу ие более 10 микросхем емкостью не менее 0,002 мкФ на микросхему. Конденсаторы устанавливают на той стороне платы, на которой располагают микросхемы. Для подведения напряжения питания и подключения шины «земля» ре- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [ 16 ] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] 0.0013 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||