|

|

Главная Линейные элементы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [ 48 ] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] считаем запертыми) и длительностью f заряда входной емкости Свх транзистора до порогового уровня, при котором он отпирается (т. е. длительностью заряда Свх от Ue, закр до f/nop = = +0,6 В; для схемы рис. 2.47 при наличии источника «б закр = = -0,6 В, а для случая, когда источник Ее исключен, ие закр ~ « 0,20,3 В). Диод Дх запирается быстро, сразу после начала спада коллекторного тока в ЦИС 1, так как обычно параметры ЦИС (к, Еа, Rk, Ra) таковы, что скорость нарастания напряжения на коллекторе ЦИС 1 (т. е. на емкости Свых) не меньше скорости нарастания напряжения в точке А (см. рис. 2.47) и на базе транзистора ЦИС 2 (т. е. на емкостях С а и входной емкости инвертора Свх). Поэтому 4 определяется практически лишь временем заряда емкости Свх + Са до порогового уровня, приблизительно равным: * -Сэкв - и пор F -Р /л-2"дсм б\. Сл = (m - 1) Сд в,-f тСд п-f Сд + С„; Сдп-емкость диод - подложка; См - емкость монтажа; (т-1)Сдвх - емкость т-1 запертых входных диодов; Сд- емкость резистора RJ. По истечении 4 формируется фронт включения ЦИС 2. Сначала напряжение на выходе ЦИС 2 падает и в некоторый момент достигает порогового уровня Ывхпор отпирания диода Дг ЦИСЗ; до этого момента диод Д1 был заперт и напряжение на коллекторе ЦИС 2 уменьшалось с постоянной времени трэкв = тр -f РьСвъш, где Свых = (Р + 1) Ске+ Ска + Свх + См -f ПаСд. Длительность рассматриваемого временного интервала t" = rsKJn--. (2.130) "вх пор По истечении t = f -j- t" входной диод Д\ открывается и начинается рассасывание заряда в базе транзистора ЦИС 3, длительность которого определяет задержку выключения з ЦИС 3. Если Б качестве Дсм используются диоды без накопления (т. е. диоды с относительно малой длительностью восстановления обратного сопротивления), то они оказываются запертыми и длительность рассасывания заряда определяется величиной обратного тока, равной {Ее + ибн)Шб- Если же используются ДНЗ, то они при выключении ЦИС 3 и и- и° остаются открытыми. Поэтому напряжение на базе транзистора ЦИС 3 Ue - Ua - 2% см < О, 152 (Оу=1,6В, ы-*ы°1=1В) и рассасывание заряда в базе идет благодаря обратному току /бзаш практически равному (2Ыд„ - -~"5i)/Bx- входное сопротивление транзистора Rbx состав- ляет десятки ом, то /бзап - десятки миллиампер, что намного превышает величину коллекторного тока запирающегося транзистора ЦИС 3, и поэтому процесс рассасывания протекает весьма быстро, так что задержка выключения 4 невелика. Очевидно, что при использовании ДНЗ в качестве смещающих диодов для создания обратного тока базы нет необходимости в источнике Ее (в таких случаях резистор Re заземляется). Среднее время задержки на одну ЦИС 4ср = (4Ч4 (2.131) Заметим, что сверх ti имеется еще задержка в росте выходного напряжения ЦИС 3, обусловленная восстановлением обратного сопротивления диода Дх ЦИС 4, нагружающего ЦИС 3. Среднее время задержки гз ср в схемах ДТЛ слабо зависит от коэффициента разветвления Пи отметим, однако, некоторое уменьшение задержки выключения ti схемы (в нашем примере - ЦИС 3) при увеличении «з, так как при этом растет ток насыщения /кнз и уменьшается степень насыщения транзистора ЦИС 3), а также увеличение t" при увеличении «2 [см. (2.130)]. К росту приводит также увеличение Ек, так как при этом растет ЕК С ростом Еа уменьшается 4ср, так как включение ЦИС 2 происходит при большем входном токе, уменьшается t°, но увеличивается ti (при большем Еа больще ток базы и, следовательно, больше степень насыщения открытого транзистора); отметим, что с увеличением Еа растет и мощность, потребляемая схемой. Варианты схем. Применение сложного инвертора Наряду с основной схемой ДТЛ (рис. 2.47) широкое распространение получили различные ее модификации, отличающиеся более высоким быстродействием, или большей нагрузочной способностью, или менее высокими требованиями к параметрам транзистора и т. п. В различных вариантах схем используются, прежде всего, различные сложные инверторы (вместо простого в основной схеме) и различные структуры цепи связи. В схеме, приведенной.на рис. 2.49, один из смещающих диодов заменен транзистором Гсм; это позволяет увеличить отпирающий ток основного транзистора /осн (или в качестве Госн использовать транзистор с меньшим р) либо увеличить коэффициент разветвления. Для уменьшения времени ti рассасывания используется ускоряющая емкость, роль которой выполняет барьерная емкость запертого диода Д. Для уменьшения tl, а также для увеличения коэффициента разветвления до значения п = 10-12 (по сравнению с п = 4-6 в основной схеме) иногда используется ключ-инвертор с нелинейной отрицательной обратной связью (см. параграф 2.5.2). Д -К- дыходоВ Рис. 2.49 На рис. 2.50а приведен широко применяемый на практике вариант сложного инвертора, благодаря которому удается повысить нагрузочную способность и быстродействие логической схемы.  Дг Рис. 2.50

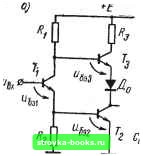

При подаче на вход сложного инвертора высокого уровня напряжения «Bx~L отпирается и насыщается транзистор Ti, отпирается транзистор Га и емкость Сн быстро разряжается большим током транзистора Т; с разрядом емкости Сн насыщается транзистор Га и на выходе инвертора появляется низкий уровень напряжения: Ивых=вых="кн=2 (заметим, что для насыщения транзисторов Г, и Гг должно выполняться условие = и, + + "бэ2 -2ыдд= 1,6В). При этом диод До обеспечивает запирание транзистора Тз. Действительно, суммарное напряжение на эмиттер-154 [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [ 48 ] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] 0.0023 |