|

|

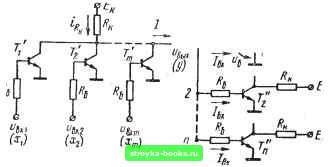

Главная Линейные элементы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [ 51 ] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] Характер переходных процессов в схеме ТТЛ в основном аналогичен характеру переходных процессов в схеме ДТЛ, особенно если в последней роль смещающих диодов Дсм выполняют ДНЗ. , Б схеме ТТЛ со сложным инвертором обеспечивается весьма быстрый режим включения. Это обусловлено, во-первых, быстрым зарядом входной емкости через малое выходное сопротивление эмиттерного повторителя инвертора предыдущего элемента, во-вторых, быстрым включением транзисторов Ti и Т2 благодаря большому току базы к (2.135) и, в-третьих, быстрым разрядом выходной емкости элемента током открывающегося транзистора Т2. Быстрое выключение ТТЛ обеспечивается, во-первых, быстрым разрядом входной емкости через открывающийся транзистор Т2 предшествующего элемента, во-вторых, быстрым включением транзисторов Т\ и Т2 благодаря тому, что накопленный в их базах заряд рассасывается большим током (замыкающимся через малые сопротивления насыщенного МТ и насыщенного транзистора 7*2 предшествующего элемента) и, в-третьих, быстрым зарядом выходной емкости через эмиттерный повторитель (транзистор Г3). Обычно, из-за этапа рассасывания задержка выключения оказывается существенно больше задержки включения Характеристики элементов ТТЛ Нагрузочная способность интегральных элементов ТТЛ со сложным инвертором обычно порядка 10-Ь 15. Коэффициент объединения по входу определяется числом эмиттеров МТ, обычно т 8; увеличение числа эмиттеров приводит, в частности, к увеличению площади, занимаемой МТ на поверхности кристалла. Быстродействие элементов ТТЛ со сложным инвертором достаточно велико; обычно 4ср 10-f-40 не. Помехоустойчивость элемента ТТЛ с простым инвертором по отношению ко входной отпирающей помехе C/J, невелика, так как невелик запас по запиранию транзистора Т. Действительно, напряжение на коллекторе МТ (при хотя бы одной открытой транзисторной структуре) порядка 0,4 В, а так как пороговый уровень С/пор 0,6 В, то запас по запиранию всего 0,2 В. При использовании сложного инвертора запас по запиранию существенно больше (порядка 0,8 В), так как пороговый уровень его отпирания (т. е. уровень отпирания транзисторов Ti и Т2) 2Lnop=l,2B. Помехоустойчивость f/n относительно запирающей помехи зависит от запаса по запиранию эмиттерных переходов МТ и может быть увеличена путем увеличения питающего напряже* ния Б. Обычно С/;п - порядка 0,51 В. Потребляемая мощность Рср в схемах ТТЛ со сложным инвертором-порядка 10 -ь30мВт. 2.6.5. ТРАНЗИСТОРНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ С РЕЗИСТИВНЫМИ И НЕПОСРЕДСТВЕННЫМИ СВЯЗЯМИ Схема Типовая схема интегрального транзисторного логического элемента с резистивными связями (РСТЛ) приведена на рис. 2.52. Схема НСТЛ (транзисторная логика с непосредственными связями) отличается от схемы РСТЛ лишь тем, что в ней отсутствуют резисторы Re; при этом сильнее сказывается разброс параметров схемы, особенно входных характеристик транзисторов (основное назначение резисторов Re и состоит в выравнивании входных характеристик открытых транзисторов).  Рис. 2.52 Рассматриваемая схема имеет т входов и п выходов и реализует логическую функцию ИЛИ - НЕ для входных сигналов положительной логики, т. е. для сигналов, низкий уровень Е° которых кодируется «О», а высокий - «1». Если обозначить через Хи Х2, .... Хт информационные значения входных переменных, и через у - значения выходной переменной, то можно записать y = Xt\/ Х2\/ V х„ (2. И 5) Статические режимы Пусть на все входы схемы поданы низкие уровни напряжения, т. е. Ыв1г== Е° Lnop; другими словами, Xi = Х2- ... = Хт = 0. При этом все транзисторы Ti, .. ., Im заперты, а транзисторы нагрузки Tl , Тп открыты и насыщены благодаря достаточной величине выходного тока /вых ступени запертых транзисторов Т. При идентичности параметров (т. е. при отсутствии разброса сопротивлений Re и напряжении Ыби на базах нагрузочных транзисторов), пренебрегая токами закрытых транзисторов (т/кзанр). можно записать --ЬтШ- (2.146) входной ток транзистора нагрузки Г Для насыщения транзисторов Т" необходимо, чтобы /вх>/б„ = /кп, (2.148) где /кн - коллекторный ток насыщенного транзистора, равный сумме тока через Як и п входных токов /бзакр закрытых транзисторов, на которые, в свою очередь, нагружены транзисторы Г"; если пренебречь величиной п/бзакр, то /кп = (к - "кп)/Рк и с учетом (2.147) условие (2.148) принимает вид к-«бн,£к (2.149) пЯк + Яб В/?к Из ф-лы (2.149), в частности, можно получить допустимое (или максимальное) значение коэффициента разветвления Лмакс- При наличии разброса параметров р, Ыбн, /?б, Rk, Ек условие (2.149) должно выполняться для наихудшего их сочетания, вследствие этого максимальный-коэффициент разветвления может существенно уменьшиться; особенно сильно на величину Пмакс влияет разброс входных характеристик, приводящий к большой неравномерности в распредЭтении базовых токов. Увеличение сопротивлений Ra способствует более равномерному распределению входных токов и, следовательно, увеличению п; однако при больших Rn может быть нарушено условие насыщения (2.149) и, кроме того, возможно уменьшение быстродействия ключевой схемы. Увеличения п„акс можно достигнуть увеличением напряжения к; минимальное значение Ек должно быть достаточным для обеспечения заданного значения п при минимальной температуре, заданном разбросе параметров и максимальной запирающей помехе, действующей на входе открытого транзистора. Заметим, что допустимый разброс входных характеристик ограничивает и максимальный коэффициент объединения по входу "макс; увеличение т ведет к уменьшению коллекторного тока насыщения транзистора (примерно равного Ек/тЯк), что, в свою очередь, приводит к уменьшению Ыбн. Выходное напряжение ступени запертых транзисторов Т «вых закр = «б н + /вхРб =Е - ПГ(2.150) представляет собой высокий уровень напряжения включающий транзисторы последующей ступени. i 6* . 163 [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [ 51 ] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] 0.0009 |