|

|

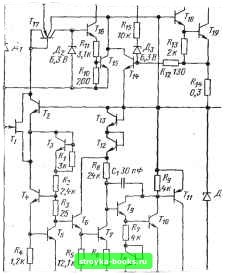

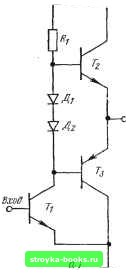

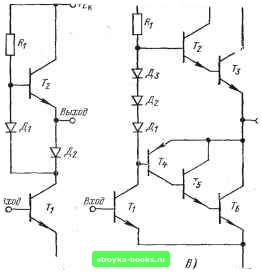

Главная Интегральный монолит [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [ 42 ] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] напряжение можно рассчитать по следующей формуле: (/вь,х=;4С/бэ +A(/63-f-, (6-11) А(/бэ={(/бз)5-((/бэ),= I 2 (6-12) Таким образом, температурный коэффициент выходного напряжения можно снизить до нуля путем выбора соотнощения сопротивлений резисторов и токов так, чтобы выполнялось равенство -?1п- дТ 4R,T (6-13) В упрощенной схеме стабилизатора на рис. 6-5 усилительный каскад образован транзисторами Ts и Тд, соединенными по схеме Дарлингтона, и боковым р-п-р транзистором Тп. Цепь обратной связи усилителя сигнала ошибки замкнута через согласующий эмиттерный повторитель на транзисторе Т. Источник тока /о задает уровень смещения на транзистор Тп с помощью транзистора Го в диодном включении. На рис. 6-6 приведена полная принципиальная схема стабилизатора, на которой показаны также и цепи защиты от перегрузок. В этой схеме источник тока /о построен на р-канальном полевом транзисторе Ti с управляющим р-п переходом. Транзистор Тп выполнен в виде одного многоколлекторного транзистора (см. рис. 4-19). Монолитный конденсатор емкостью 30 пФ используется для частотной коррекции усилителя сигнала ошибки. Транзистор Гц р-п-р типа, в котором подложка служит в качестве коллекторной области, введен для дополнительного повышения коэффициента усиления усилителя сигнала ошибки. Стабилитроны Д1 и Дз обеспечивают защиту входных и выходных цепей стабилизатора от повышенных напряжений, которые могут возникать в переходном режиме. Рассматриваемая схема стабилизатора обеспечивает токи в нагрузке до 1,5 А. Так как выходной ток полностью проходит через последовательный элемент, в качестве которого в схеме рис. 6-6 служит транзистор Гю, этот транзистор занимает на монолитной пластинке больше места, чем все остальные элементы схемы стабилизатора. Вопросы проектирования и размещения транзисторов таких больших размеров и их характеристики рассматриваются ниже в § 6-5. Схема стабилизатора, показанная на рис. 6-6, предназначена для работы при входных напряжениях от 7 до 35 В и обеспечивает выходные токи в диапазоне от 5 мА до 1,5 А. Ниже приведены типовые электрические характеристики схемы стабилизатора для выходного напряжения 5 В. Типовые электрически? характеристики [стабилизатора напряжения LMI09 Коэффициент стабилизации по напряжению (при изменении входного напряжения в диапазоне от 7 до 25 В).....0,1% t/obK Коэффициент стаби.вдзации от юздействия нагрузки (при изменении тока нагрузки в диапазонг от 5 мА до 1,5 А) 1% вых Коэффициент Ослабления пульсаций ........... 80 дБ Температурный коэффициент выходного напряжения . . . 0,010Уо иа 1°С Потребляемый ток холостого хода............ 5,2 мА Диапазон входного напряжения . От 7 до 35 В Выходное напряжение . . . . 5,05 В Максимальный выходной ток . 1,5 А Так как схема предназначена для стабилизации напряжения при больших уровнях мощности, поэтому в ее составе содержится устройство зашиты от перегрева, включающее диод Да и транзисторы Та и Tie, которое отключает схему стабилизатора, если внутренняя температура р-п переходов превышает максимально допустимую величину (как правило, 175±10°С). Принцип Вход Выход  fiJB Звмлл Рис. 6-6. Полная принципиальная схема стабилизатора напряжения г7вых=5 В типа LM109. действия схемы тепловой защиты будет рассмотрен в § 6-4. Так как для работы схемы стабилизатора не требуется подключения внешних элементов, она имеет только три вывода. Следовательно, схему такого стабилизатора можно помещать в сравнительно недорогой корпус с тремя выводами, предназначенный для мощных транзисторов типа ТО-3, который имеет очень малое тепловое сопротивление, порядка 1,5°С/Вт. Две схемы монолитных стабилизаторов напряжения, рассмотренные в качестве примеров в настоящем параграфе, были выбраны с щелью, чтобы проиллюстрировать основные методы проектирования схем такого типа И показать характеристики .существующих интегральных стабилизаторов напряжения. Кроме того, эти примеры иллюстрируют подход к выбору схем стабилизаторов при их проектировании, т. е. проектировать наиболее универсальную схему для разнообразных применений или пытаться оптимизировать схему для специального применения. Так, схе- ма, приведенная на рис. 6-4, является универсальной, и поэтому для ее работы требуются некоторые дополнительные внешние выводы. Схема; стабилизатора рнс. 6-6 предназначена для использования только в цифровых системах, и все необходимые элементы управления и зашитьт расположены на той же интегральной.пластинке, которая имеет всего-три внешних вывода: ,вход, выход и-заземление. 6-3. УСИЛИТЕЛИ мощности Усилители мощности предназначены для передачи больших мощностей синусоидального колебания бе» искажений в низкоомную нагрузку. Основные требования, которые были рассмотрены применительно к схемам мощных стабилизаторов,, относятся также и к схемам монолитных усилителей мощности. Особенно это справедливо по отношению к схемам защиты, необходимым для устранения отказов, связанных с тепловыми или электрическими перегрузка.ми. От усилителя мощности требуется, чтобы он передавал номинальную мощность, при малых нелинейных искажениях, на выходе и .при минимальных потерях мощности. Кроме того, к схеме усилителя мощности предъявляется требование хорошего сглаживания пульсаций напряжения,, что .позволяет использовать для питания усилителя сравнительно плохо стабилизированные источник» постоянного тока. Требование линейности может быть удовлетворено путем применения местных обратных связей илк обратной связи, охватывающей все-усилительные каскады. Небольшие-потери -мощности можно обеспечить, благодаря работе мощных выходных каскадов в режиме класса Б или АБ. Основная проблема, возникающая при проектировании и изготовлении монолитных усилителей мощности, связана с недостатками: технологических процессов. Для из- готовления выходного каскада, ра-«ботающего в режиме класса Б и имеющего хорошие характеристики, требуется в его схеме иметь транзи--сторы как п-р-п, так и р-п~р типа, причем параметры транзисторов обоих типов должны быть примерно одинаковыми. Однако боковые транзисторы р-п-р типа и с использованием подложки в качестве кол-.лекторной области, .которые можно изготовить одновременно с транзисторами п-р-п типа на одной монолитной пластинке, имеют недостаточно хорошие частотные характеристики, и их коэффициент усиления по току очень быстро падает при больших токах. Последнее обусловлено главным образом тем обстоятельством, что базовая и эмиттерная области этих транзисторов имеют малую концентрацию носителей. На рис. 6-7 приведены три основные схемы выходных каскадов, работающие в классе Б, которые могут использоваться в качестве усилителей мощности. Схема рис. 6-7,с представляет собой обычный каскад, работающий в классе Б, который применяется в цифровых устройствах, где необходимо ис- пользовать мощные транзисторы р-п-р и п-р-п типов. В схемах рис. 6-7,6 и в не требуются мощные дополнительные транзисторы р-п-р типа, и поэтому их можно изготовить в монолитной форме, используя планарную технологию, которая применяется для производства интегральных схем с биполярными транзисторами п-р-п типа. Схема рис. 6-7,6 является двухтактной схемой, которая была описана в гл. 5 (см. § 5-4). Недостатком такого каскада является асимметрия усиления напряжения, которая проявляется в искажении отрицательной полуволны сигнала. Схема рис. 6-7,в является модифицированным вариантом выходного каскада, работающего в классе Б, рис. 6-7,0. Мощный транзистор п-р-п типа в схеме на дискретных элементах образован двумя транзисторами Гг и Гз, соединенными по схеме Дарлингтона. Аналогичным образом мощный транзистор р-п-р типа имитируется боковым транзистором р-п-р и еще двумя транзисторами п-р-п типа Г5 и Гб, также соединенными по схеме Дарлингтона. Такое соединение трех транзисторов аналогично описанному  Выход  Выход Рис. 6-7. Основные схемы выходных усилительных каскадов. [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [ 42 ] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] 0.0011 |