|

|

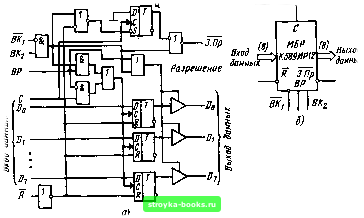

Главная Микропроцессорные системы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [ 88 ] [89] [90] [91] [92] Бдд)ер данных Чт ве/выв Зп Вв/Выв tUHXp С5рос Ад-Аз Готов Захв П-Захв Чт.ЗУ Зп.ЗУ Р. Ад Ст. Ад Марк Логика Чт/Зп У У и регистр ХистаноВки \ режима Внутренняя шина Канала Счетчик адреса 16 разр. -1- -ЗРДП-0 -ппдп-0 Канал 1 Счетчик адреса 16разр. zzi- Канав 2 Счетчик адреса 1бразр. КаналЗ Счетчик адреса 1бразр. -ЗПДП-1 ППДП-1 -ЗПДП-1 -ппдп-г ЩП-3 Приоритетное устройство Рис. П.8. Функциональная схема программируемого устройства ПДП типа К580ИК57 Программируемое устройство прямого доступа в память типа К580ИК57. Устройство представляет собой 4-канальный контроллер, используемый в МП системах, построенных на основе ЦПЭ К580ИК80. Эта микросхема после программного обращения к ней ЦПЭ может осуществлять передачу массивов данных обтемов до 16 Кбайт между ЗУ и ВУ без участия ЦПЭ. По запросу на ПДП, полученному микросхемой К580ИК57 от ВУ, она выполняет следующие функции: берет на себя управление системой шин, подтверждает запрос ВУ, подключенного к каналу с наивысшим приоритетом, выдает 8 младших разрядов адреса памяти на общие адресные линии A-Ло, а 8 старших разрядов в регистр памяти ВУ, генерирует соответствующие сигиалы управления, органнзую-щие передачу или прием 8-разрядного слова между ЗУ и ВУ. Функциональная схема программируемого устройства ПДП приведена на рис. П.8. Микросхема может работать в одном нз трех различных режимов. 1. Режим чтения при ПДП, который обеспечивает передачу данных нз ЗУ в ВУ. 2. Реясим записи ПДП, который обеспечивает передаду данных из ВУ в ЗУ. 3. Режим проверки ПДП, прн котором передача данных не происходит. Поясним назначение отдельных выводов микросхемы. Dj-Dj - шина данных, связывающая ЦПЭ с ВУ. Чт.Бв-Выв (Чтение Ввод-Вывод) - управляющий вход - выход, который: а) разрешает считывание содержимого регистра состояния старшего (младшего) байта регистра адреса ПДП или регистра «Конец счета» и б) разрешает считывание данных нз ВУ в цикле записи ПДП. Зп.Вв-Выв Запись Ввод - Вывод - управляющий вход - вы-%ож, используемый для разрешения записи сигналов в регистры состояния, адреса ПДП или «Конец счета», а также для записи дан-дых в ВУ в течение цикла чтения ПДП. Синхр (Синхронизация) -вход тактовой последовательности импульсов Фг. Сброс - сигнал, приводящий микросхему в исходное состояние. Лз-Ло - младшие разряды шины адреса, используемые либо .для выбора регистра памяти ВУ, либо для установки младших разрядов Д 6-разрядного регистра адреса памяти. By (Выбор устройства) - сигнал выбора данной микросхемы. Л?-Л4 - старшие разряды шины адреса, используемые для установки соответствующих разрядов регистра адреса памяти во время всех циклов ПДП. Готов (Готовность) - управляющий вход, используемый для удлинения циклов чтения и записи в ЗУ путем перевода К580ИК57 В состояние ожидания. Такой режим применяется в то.м случае, когда ЗУ требует более длинных циклов. З.Захв (Запрос захвата)-выходной сигнал, подаваемый на соответствующий вход ЦПЭ К580ИК80. П.Захв (Подтверждение захвата) - входной сигнал от ЦПЭ К580ИК80, подтверждающий, что все шнны МП приведены в состо--янне высокого сопротивления. Чт.ЗУ (Чтение ЗУ) - выход, используемый для чтения данных •3 адресуемых ячеек памяти в течение циклов чтения ПДП. Зп.ЗУ (Запись ЗУ) - выход, используемый для записи данных # адресуемую ячейку ЗУ во время циклов записи ПДП. Р.Ад (Разрешение адреса) - выход, используемый для отклю-.чеиня шины данных управлення данной микросхемы от соответствующих системных шин. Ст.Ад (Строб адреса) - управляющий сигнал, осуществляющий лтробированне старшего байта адреса памяти, передаваемого через :*инну данных в регистр памяти ВУ. КС (Конец счета) - выходной сигнал, указывающий вубранно-:му в данный момент ВУ, что текущий цикл ПДП является послед-:ним циклом для этого массива данных. Марк (Маркер по модулю 128) - выходной сигнал, указываю-данй выбранно.му ВУ, что текущий цикл ПДП является по порядку 128-м циклом от момента появления предыдущего сигнала «Марк». ЗПДП-0-ЗПДП-3 (Запрос ПДП) - входы, используемые ВУ для получения цикла ПДП. ППДП-0-ППДП-3 (Подтверждение ПДП) - выходной сигнал микросхемы, информирующий ВУ, подсоединенное к данному каналу, что оно выбрано для ПДП цикла. П.З. МНОГОРЕЖИМНЫЙ БУФЕРНЫЙ РЕГИСТР (МБР) К589ИР12 МБР (рис. П. 9,а, б) представляет собой БИС с тремя выходными состояниями, предназначенную для использования в качестве устройства ввода - вывода или буферного регистра ВУ. Элементами памяти МБР служат 8 Д-трнггеров, каждый из ко-  Рис. П.9. Функциональная схема и условное обозначение МБР типа К589ИР12 торых имеет асинхронный вход установки нуля R. Выходы D-триг-геров соединены с выходными иеинвертирующими буферными схемами, имеющими три состояния и управляемыми виутреиними сигналами «Разрешение». Управляющие входы, BKi и ВКг (Выбор кристалла) используе-ются для выбора даииой схемы МБР по выходу дешифратора шины адреса. При BKi5=0 и ВКа=1 выходные буферы отпираются, а триггер сигналов запроса прерывания устанавливается в единичное состояние. Вход BP (Выбор режима) определяет режим работы МБР. При ВР=1 имеет место режим вывода информации Из МБР, и в качестве сигналов синхронизации для выходных Д-триггеров используются сигналы ВК1ЛВК2. При ВР=0 в МБР осуществляется ввод данных, а в качестве сигналов синхронизации используются сигиалы, подаваемые иа вход С (Строб) МБР. По этим сигналам [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [ 88 ] [89] [90] [91] [92] 0.0011 |